CLEAR est un microcontrôleur RISC-V (VexRISCV) muni d’un eFPGA gravé en 130 nm et produit avec le programme chipignite de la société de production d'ASIC Efabless. La totalité du « dossier de fabrication » du composant est publiée (licences MIT, Apache 2.0 et d'autres moins non libres).

Sommaire

- openFPGA : le générateur de FPGA

- Caravel : embarquez votre composant avec un processeur RISC-V

- Chipignite : les ASIC pour tous

- Sky130 : le « kit ASIC » (pdk) libéré

- Open MPW shuttle : les ASIC open source gratuits de Google

- La production de CLEAR en financement participatif

Un FPGA est un type particulier de composant électronique. Il peut être vu comme un « kit » de portes logiques avec des connexions reconfigurables à l’infini. Le tout est assemblé dans un même composant. Les constructeurs de FPGA gardent jalousement secrète une partie de l’architecture de leurs composants et ne fournissent même pas la documentation permettant de les configurer. Il est nécessaire de passer par leurs logiciels (binaires) pour générer le fichier de configuration appelé bitstream.

La conception et la fabrication d’un FPGA passent par les mêmes procédés que pour n’importe quel composant électronique numérique (processeur, périphérique, microprocesseur) : on part d’un modèle numérique du composant que l’on va transformer en un dessin « 3D » du circuit final appelé GDSII. Toute cette chaîne de fabrication utilise un tas de formats et de standards jalousement gardés secrets par les différents acteurs de cette industrie. Il est évident que les fabricants de FPGA gardent secret ces « dossiers de fabrication ».

Il y a quelques années, Claire Clifford libérait le format des bitstreams de configuration du FPGA ice40 par rétro-ingénierie avec le projet Icestorm. D’autres FPGA ont ensuite été libérés par ingénierie inverse, sans soutien des différents constructeurs.

Un pas de plus dans la libération des FPGA a été franchi avec la production du EOS S3 de la société QuickLogic. QuickLogic a publié le format du bitstream de la partie FPGA (eFPGA) de son composant et supporte officiellement les outils opensource.

Avec le CLEAR, on passe à une toute autre échelle de libération pour les FPGA. En effet — cette fois — c’est la totalité du « dossier de fabrication » qui est libéré. Commençons par le cœur du composant : openFPGA.

openFPGA : le générateur de FPGA

L’architecture utilisée dans le CLEAR est celle du projet openFPGA. Le projet propose de générer une structure de FPGA « prête à graver » à partir d’un simple fichier de configuration de l’architecture voulue. L’objectif étant de réduire le temps de développement d’un FPGA à 24 heures, au lieu des mois habituels.

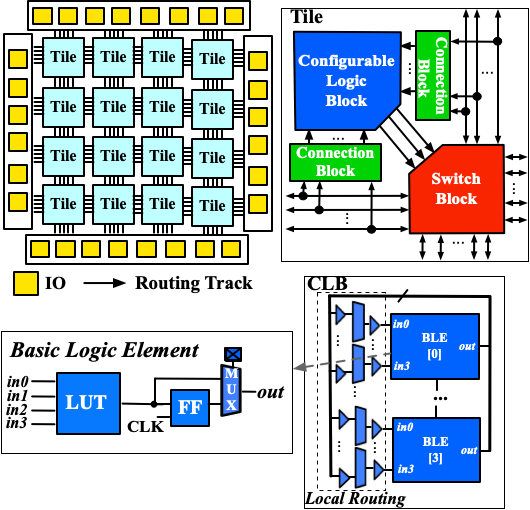

L’architecture du eFPGA est constituée de 8 × 8 = 64 CLB. Chaque CLB contient quatre Blocs Logique Élémentaire (BLE) avec à chaque fois :

Ce type d’architecture se retrouve dans tous les FPGA avec une variation sur le nombre d’entrées de la LUT. Cela nous permet de comparer les FPGA en termes de nombre de LUT.

Avec le CLEAR nous avons donc un eFPGA de 256 LUT. Pour comparer on peut parler du EOS S3 qui possède 891 LUT ou du ICE40 dont la gamme débute à 384 LUT et monte jusqu’à environ 8000 LUT.

On parle donc d’un tout petit eFPGA. Avec une architecture de FPGA open source (MIT pour OpenFPGA), il est plus évident de développer des outils libres pour travailler sur ces FPGA. L’outil de référence pour configurer les FPGA générés avec openFPGA est issu majoritairement du projet VTR (Verilog To Routing).

La partie FPGA ainsi générée est prête à être intégrée dans la caravelle.

Caravel : embarquez votre composant avec un processeur RISC-V

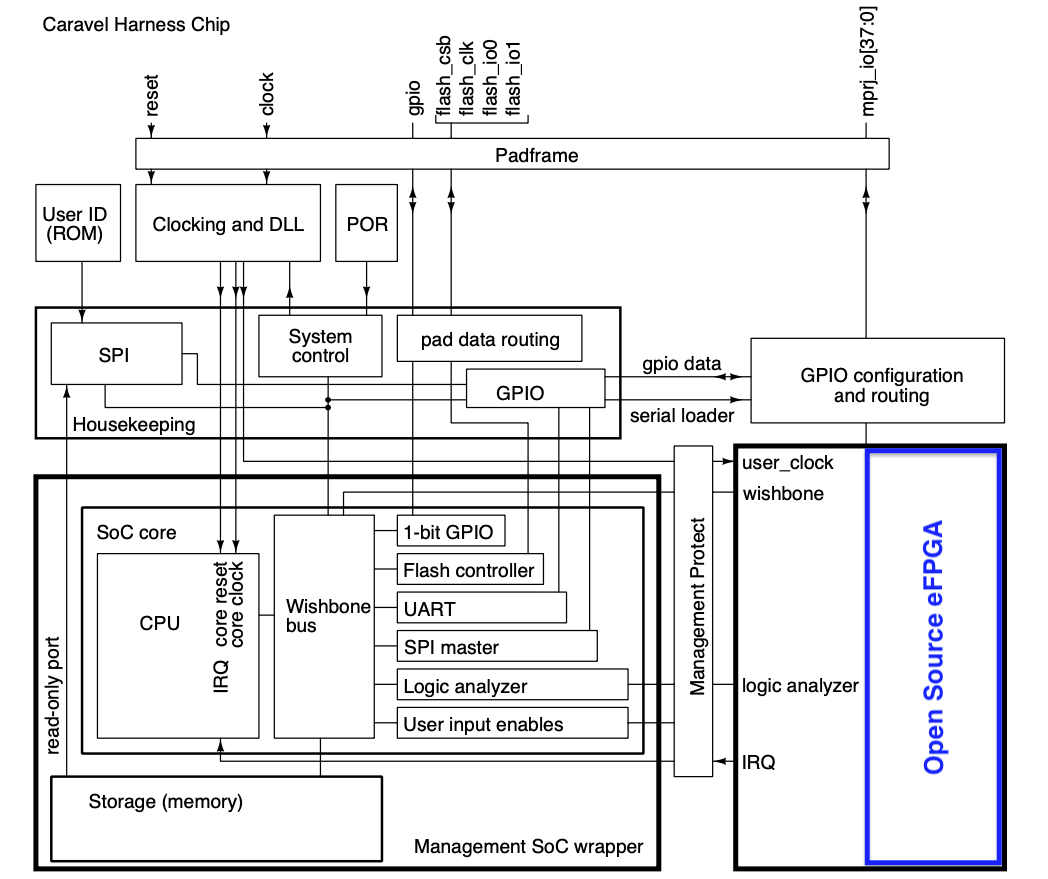

La lectrice ou le lecteur aura certainement remarqué que le titre de la dépêche ne parle pas de FPGA mais de eFPGA. e qui signifie simplement « embedded ». Le FPGA généré est embarqué dans un composant plus gros muni d’un microprocesseur 32 bits nommé VexRisc qui est open source (MIT) lui aussi.

Ce processeur — développé par Charles Papon avec le langage HDL SpinalHDL — est la base du SoC Caravel développé par la société eFabless et open source lui aussi (APLv2).

L’objectif de Caravel est de proposer un SoC complet avec le CPU, quelques périphériques (UART, SPI, GPIO, RAM…) et une zone libre pour y graver un composant de son cru. Toute la partie « outils de déverminage » est ainsi standardisée avec tous les signaux nécessaires au bon fonctionnement du projet cible.

Avec cet outil, efabless veut démocratiser la fabrication de composant électronique et la rendre accessible aux petites PME, voire aux particuliers.

Ce kit de développement est proposé par la société efabless avec son programme chipignite.

Chipignite : les ASIC pour tous

Avec le programme Chipignite d’efabless, il est en effet possible de faire produire 100 composants (ou 300 selon le boîtier choisi) pour moins de 10 000 $ gravé en 130 nm.

À ce prix-là, on a tous les outils de développement à disposition ainsi que les bibliothèques du kit de développement (PDK) en 130 nm du fabricant, sans avoir à signer d’accord de non divulgation (NDA) pour lire l’accord de non divulgation à signer.

Comme le nom de la société le laisse entendre, efabless ne possède pas d’usine de fabrication. Elle se contente de réserver des slots (shuttle) de fabrication dans l’usine américaine skywater.

Sky130 : le « kit ASIC » (pdk) libéré

Skywater est un petit fabricant de composants électroniques américain. C’est une ancienne usine de Cypress qui a pris son indépendance.

Cette entreprise fabrique des semi-conducteurs à des niveaux de gravure qui sont aujourd’hui considérés comme largement amortis. Le 130 nm par exemple est la finesse de gravure utilisée il y a 20 ans pour les processeurs Pentium III ou pour le processeur de la Gamecube.

Pour faire produire un composant électronique, il faut fournir un fichier de fabrication au format GDSII. Qui est un format ouvert de description des différentes couches de dopage et de connexions métal du composant.

Mais pour générer ce GDSII, l’entreprise qui conçoit des composants a besoin de connaître les propriétés du substrat fabriqué. Il faut un modèle pour simuler les composants que l’on « dessine ».

À partir de ce modèle il est possible d’établir une bibliothèque de composants comme des transistors, bascules, mémoire et autres.

Toutes ces informations sont rassemblées dans ce qu’on appelle un PDK (Process Design Kit). Le PDK est intimement lié au fabricant et au process de fabrication. Sans lui, impossible de concevoir et générer le GDSII, malgré la disponibilité de nombreux (et vieux) logiciels libres dans le domaine.

Jusqu’à l’année dernière, il n’existait pas de PDK « ouvert » : impossible pour une petite entreprise d’y avoir accès sans payer des sommes folles en licences de développement. Sans compter sur les accords de non divulgation qui rendaient impossible la diffusion du GDSII en dehors de la production.

Pour dynamiser sa production, Skywater a donc décidé, avec l’aide de Google, de libérer son PDK pour la finesse de gravure de 130 nm. Le PDK se nomme Sky130 et est disponible à tous sous licence Apache 2.0 sur github.

Open MPW shuttle : les ASIC open source gratuits de Google

10 000 $ ça ne se trouve pas sous le sabot d’un cheval. Il y a intérêt d’avoir un projet un peu plus solide qu’un simple TapTempo. Une PME peut prendre des risques avec cette somme mais de manière mesurée.

Pour favoriser l’émergence d’une communauté open source dans le développement matériel et pour encourager les développeuses et développeurs à prendre des risques et innover, Google a décidé de financer des productions de composants tous les six mois.

Pour être dans la « navette » nommée Open MPW shuttle il faut proposer un composant totalement open source et publier tous les scripts permettant de re-générer le GDSII.

Si le projet est jugé intéressant, efabless fera fabriquer une série de composants gratuitement.

Et c’est ce qui s’est passé avec le projet Caravel-OpenFPGA-EF qui a été produit dans la première navette MPW-1.

OpenFPGA a également été utilisé dans la seconde navette MPW-2 avec le projet SOFA.

Il y a d’autre projet de eFPGA dans les navettes, mais OpenFPGA semble être le plus utilisé et le plus facile d’accès.

La production de CLEAR en financement participatif

NdM: la question de savoir si l'intégralité de l'eFPGA est open source (au sens OSI) / libre est discutée dans les commentaires. Le financement participatif l'annonce comme tel en tout cas, The Open Source FPGA ASIC.

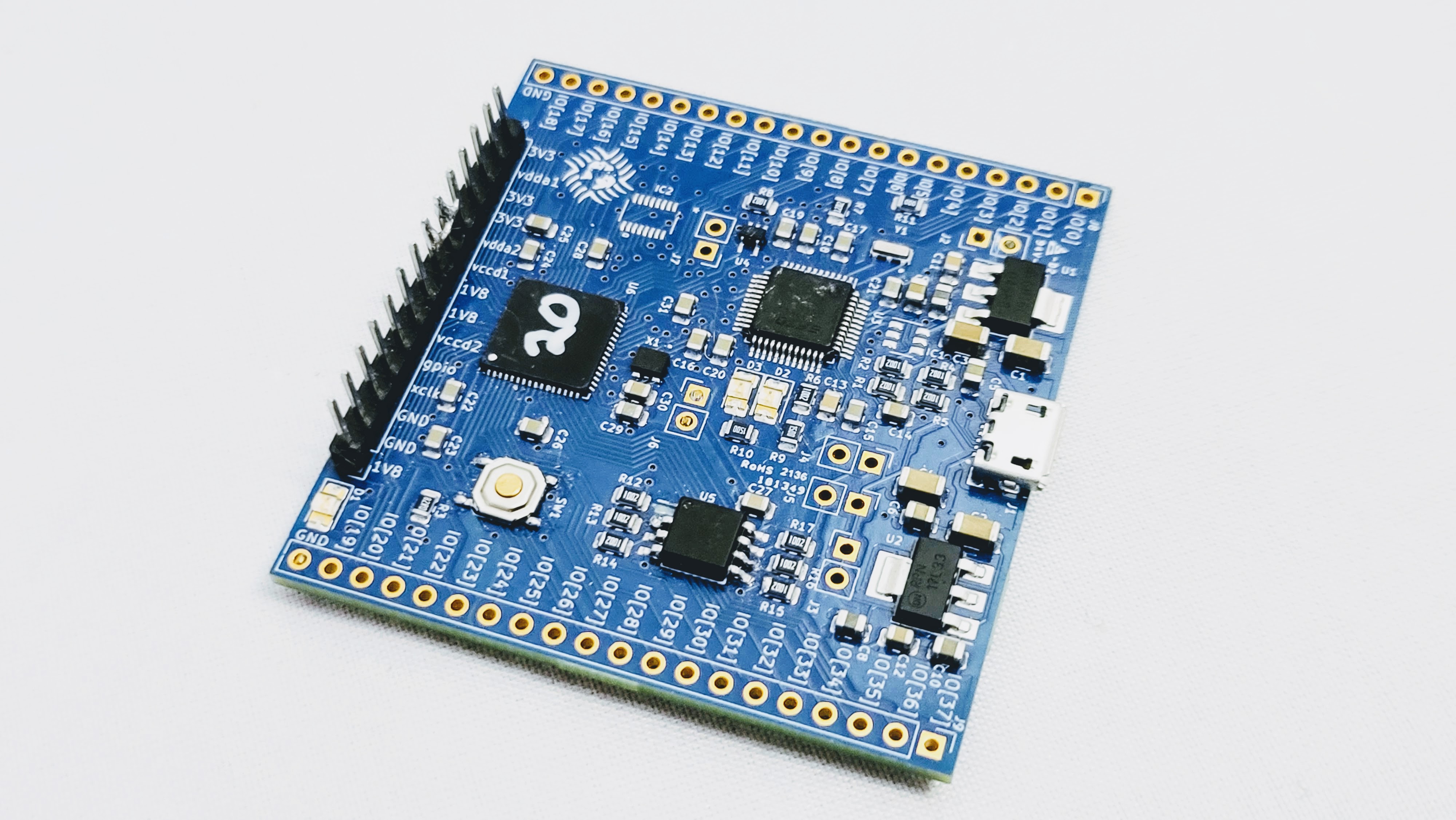

Pour montrer la possibilité de produire un eFPGA open source un financement participatif a été lancé sur le site groupgets.

Moyennant 75 $ (plus les frais de port plus certainement la douane) il est possible d’acquérir ce microcontrôleur soudé sur une carte de développement.

Une fois la levée de fonds bouclée, le projet sera embarqué dans la navette 2204C pour une production prévue en avril 2022.

Bien sûr, une carte de développement à ce prix pour un eFPGA aussi petit peut sembler inintéressante. Il faut plutôt le voir comme une somme accessible à (presque) tout le monde pour entrer dans le monde du silicium et des FPGA open source. C’est, en tout cas la preuve, qu’il est possible de produire un FPGA (+ microcontrôleur) intégralement open source à des tarifs raisonnables.

Aller plus loin

- Campagne de financement participatif du CLEAR (232 clics)

- Article de CNX Software sur l'initiative (69 clics)

- openFPGA: Le générateur open source de FPGA (82 clics)

- Caravel: le SoC open source de efabless qui embarque une « zone ASIC vierge » (62 clics)

- Sky130: le PDK open source pour graver en 130nm (65 clics)

# Intéressant

Posté par PenguinLux . Évalué à 3.

Le projet à l'air hyper intéressant !

# envie de participer

Posté par vpinon . Évalué à 7.

Merci pour cette dépêche et toute ta veille sur les IC open source (à mentionner la newsletter de librecores ?)

Je trouve très chouette l'initiative d'eFabless depuis le début, et là ça commence à vraiment donner quelque chose.

Je sais faire de l'analog/RF, mais je n'ai pas encore repéré de projet à rejoindre, ni je n'ai d'idée de truc cool à proposer (de la connectivité BlueTooth/WiFi ? Même avec de veilles versions des standards, il faut du monde pour faire les demod+MAC…)

Et sinon efabless annonce que tout est open source, mais je n'arrive pas à reproduire l'environnement de design sur ma machine : je n'ai pas trouvé leur outil de caractérisation (qui fait référence avant toute soumission lors de le leurs concours), pas plus leur intégration du PDK dans electric/xschem/ngspice ; ils utilisent un visualiseur de courbes propriétaire… a suivre ?

[^] # Re: envie de participer

Posté par bobo38 . Évalué à 3. Dernière modification le 16 février 2022 à 23:49.

https://www.youtube.com/watch?v=EczW2IWdnOM

Si je me souviens bien cette vidéo c'est un gonze de Google qui parle de PDK et des outils libres de conception de circuit, qui sont supportés par le PDK en question. Ça avait l'air bien cool. De souvenir plusieurs logiciel libre de conception de circuit on l'air d'être supportés avec leur fichier de configuration relatif à la techno 130nm dont il est question.

Les standard cells c'est des terrains de foot. Le compilateur SRAM a l'air de ne pas être trop trop optimisé en densité. Mais bon ce sont de bons legos, libres, avec lesquels faire de chouettes bricolage.

Côté design analog-RF, il y a peut-être moyen de faire un chip pour la communauté radio-amateurs. Je ne sais pas trop ce qui pourrait être cool et approprié… je vais peut-être dire une connerie : un DSP (Digital Signal Processor) qui visent les fréquences radio amateur ? ou une puce un peu flexible dont on peut changer les plages de fonctionnement avec des composants externes ? selon le scénario ça pourrait peut-être être cool d'avoir un micro-controlleur comme celui présenté ou même reprendre le FPGA pour faire du traitement du signal numérique en temps réel…

Désolé si j'ai écrit des conneries. J'avais lu ce bouquin (https://www.eyrolles.com/Sciences/Livre/le-radioamateur-9782710811848/) et j'avais été fasciné par la bande latérale unique entre autres…

# Du coup pas complètement open source / libre?

Posté par Zenitram (site web personnel) . Évalué à 8. Dernière modification le 17 février 2022 à 09:18.

Je ne connais pas de licence non libre qui seraient open source puisque la définition est la même quand on enlève le côté "marketing", pas très cohérent, du coup c'est complètement open source / libre ou "fortement open source mais pas complètement"?

[^] # Re: Du coup pas complètement open source / libre?

Posté par flavien75 . Évalué à 6.

Ça se trouve régulièrement dans les bibliothèques fournis par les fabricants de microcontrôleurs.

Par exemple chez Texas Instruments, on peut trouver en en-tête des sources:

// Texas Instruments (TI) is supplying this software for use solely and

// exclusively on TI's microcontroller products. The software is owned by

// TI and/or its suppliers, and is protected under applicable copyright

// laws. You may not combine this software with "viral" open-source

// software in order to form a larger program.

C'est open-source, on peut auditer, corriger, mais c'est quand même pas libre.

A moins que tu ne penses à l'open source dans le sens de l'OSI, mais là il faudra attendre demain.

Les vrais naviguent en -42

[^] # Re: Du coup pas complètement open source / libre?

Posté par aiolos . Évalué à 7. Dernière modification le 17 février 2022 à 09:59.

Ben, c'est pas open-source cette licence…

C'est pas parce que tu as les sources, même de manière publique publique, que c'est open-source au sens communément admis.

https://opensource.org/faq#free-software

[^] # Re: Du coup pas complètement open source / libre?

Posté par Zenitram (site web personnel) . Évalué à 8. Dernière modification le 17 février 2022 à 10:07.

Pas libre donc pas open source, cette phrase synonyme de "C'est open-source, on peut auditer, corriger, mais c'est quand même pas open-source" est aussi incohérente que la phrase de la dépêche.

Je croyais qu'on était sur un site qui promeut le libre et donc l'open source défini par l'OSI en évitant de parler d'open source défini par d'autres quand ça les arrange, et que donc la définition de open source citée dans le titre était celle de l'OSI.

C'est trompeur et LinuxFr participe du coup à l'amalgame que le libre (car le mot open source est synonyme de libre, surtout en anglais) n'est pas les 4 libertés…

[^] # Re: Du coup pas complètement open source / libre?

Posté par orfenor . Évalué à 7. Dernière modification le 17 février 2022 à 14:09.

Pas d'accord. Je suis tombé souvent sur open-source employé au sens littéral (sources ouvertes, donc consultables), en France et dans les pays anglo-saxon. On vit dans des communautés, au sens de «qui se ressemble, s'assemble», mais il faut en sortir. C'est trompeur pour toi et les gens qui te ressemblent, ça ne l'est pas pour un tas d'autres. Et c'est bien ce que flavien75 dit :

Ceux qui bossent avec ces microcontrôleurs comprennent très bien le sens.

Maintenant si on ne doit employer qu'un seul sens sur linuxfr il ne va plus rester grand monde. Déjà qu'il y a peu de dépêches.

[^] # Re: Du coup pas complètement open source / libre?

Posté par Zenitram (site web personnel) . Évalué à 6. Dernière modification le 17 février 2022 à 15:06.

Perso le non open source me va et la dépêche a du sens pour le degré d'ouverture par rapport à l'actuel, c'était juste afficher "open source" pour quelque chose qui ne l'est pas qui me dérangeait. Comme les oeuvres de l'esprit (textes, dessins…) non libres ne me dérangent pas du moment où on ne sous-entend pas que le NC est dans l'esprit du libre comme certains voudraient le (faire) croire ;-).

Et la correction apportée est très bonne : c'est affiché ici (à défaut de pouvoir corriger ailleurs) pas libre / open source mais c'est plus ouvert que les autres donc intéressant. Mais dommage que ce ne soit pas open source :-p (RISC-V, base de la chose, étant lui open source).

[^] # Re: Du coup pas complètement open source / libre?

Posté par flavien75 . Évalué à 3. Dernière modification le 17 février 2022 à 19:52.

Dans le fond, je suis d'accord avec toi, mais le problème est que "open-source" peut amener une confusion alors que le terme "libre" est sans ambiguïté.

C'est déjà pas facile de faire comprendre l'intérêt des logiciels libres à des néophytes ou des décideurs, si en plus on prend des termes ambigus, on est pas sorti.

Les vrais naviguent en -42

[^] # Re: Du coup pas complètement open source / libre?

Posté par Benoît Sibaud (site web personnel) . Évalué à 6.

Merci, j'ai modifié la dépêche dans ce sens (notamment le titre, l'ajout d'une NdM, et le rajout de licences par endroits).

[^] # Re: Du coup pas complètement open source / libre?

Posté par GuieA_7 (site web personnel) . Évalué à 4.

De souvenir, il y a quelques années une personne avait demandé de l'aide dans le forum pour trouver une licence qui oblige à envoyer les patches à l'upstream ; nous en avons trouvé une nommée RPL il me semble, qui était listée comme OpenSource par le site de l'OSI, mais pas considérée comme libre par la FSF/Debian…

On parle évidemment de licences assez obscures, les licences majeures qui représente 99.9% des cas d'utilisations n'ont pas ce souci.

[^] # Re: Du coup pas complètement open source / libre?

Posté par Gil Cot ✔ (site web personnel, Mastodon) . Évalué à 4.

Ça pique…

v1.1 https://opensource.org/licenses/RPL-1.1

v1.5 https://opensource.org/licenses/RPL-1.5

“It is seldom that liberty of any kind is lost all at once.” ― David Hume

Suivre le flux des commentaires

Note : les commentaires appartiennent à celles et ceux qui les ont postés. Nous n’en sommes pas responsables.